# Serial-Port 16-Bit SoundPort<sup>®</sup> Stereo Codec

# AD1849K

#### FEATURES

Single-Chip Integrated ∑∆ Digital Audio Stereo Codec Multiple Channels of Stereo Input and Output Digital Signal Mixing On-Chip Speaker and Headphone Drive Capability Programmable Gain and Attenuation On-Chip Signal Filters Digital Interpolation and Decimation Analog Output Low-Pass Sample Rates from 5.5 kHz to 48 kHz 44-Lead PLCC Package Operation from 5 V and Mixed 5 V/3.3 V Supplies Serial Interface Compatible with ADSP-21xx Fixed-Point DSµPs Compatible with CS4215 (See Text)

#### **PRODUCT OVERVIEW**

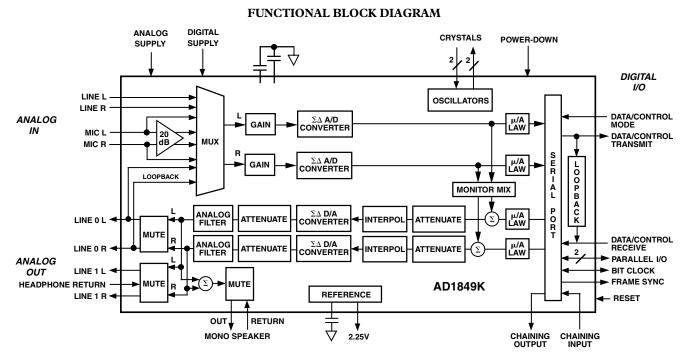

The Serial-Port AD1849K SoundPort Stereo Codec integrates the key audio data conversion and control functions into a single integrated circuit. The AD1849K is intended to provide a complete, single-chip audio solution for multimedia applications requiring operation from a single 5 V supply. External signal path circuit requirements are limited to three low tolerance capacitors for line level applications; anti-imaging filters are incorporated on-chip. The AD1849K includes on-chip monaural (mono) speaker and stereo headphone drive circuits that require no additional external components. Dynamic range exceeds 80 dB over the 20 kHz audio band. Sample rates from 5.5 kHz to 48 kHz are supported from external crystals, from an external clock, or from the serial interface bit clock.

The Codec includes a stereo pair of  $\Sigma \Delta$  analog-to-digital converters and a stereo pair of  $\Sigma \Delta$  digital-to-analog converters. Analog signals can be input at line levels or microphone levels. A software controlled programmable gain stage allows independent gain for each channel going into the ADC. The ADCs' output can be digitally mixed with the DACs' input.

The left and right channel 16-bit outputs from the ADCs are available over a single bidirectional serial interface that also supports 16-bit digital input to the DACs and control information. The AD1849K can accept and generate 8-bit  $\mu$ -law or A-law companded digital data.

The  $\Sigma\Delta$  DACs are preceded by a digital interpolation filter. An attenuator provides independent user volume control over each DAC channel. Nyquist images and shaped quantization noise are removed from the DACs' analog stereo output by on-chip switched-capacitor and continuous-time filters. Two independent stereo pairs of line-level (or one line-level and one headphone) outputs are generated, as well as drive for a monaural speaker.

SoundPort is a registered trademark of Analog Devices, Inc.

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2000

# AD1849K—SPECIFICATIONS ELECTRICAL SPECIFICATIONS

## STANDARD TEST CONDITIONS UNLESS OTHERWISE NOTED

| Temperature<br>Digital Supply (V <sub>DD</sub> )<br>Analog Supply (V <sub>CC</sub> ) | 25<br>5.0<br>5.0          | °C<br>V<br>V |

|--------------------------------------------------------------------------------------|---------------------------|--------------|

| Clock (SCLK)<br>Master Mode                                                          | 256<br>256 Pite non Frame | Fs           |

| Word Rate $(F_s)$                                                                    | 256 Bits per Frame<br>48  | kHz          |

| Input Signal                                                                         | 1                         | kHz          |

| Analog Output Passband                                                               | 20 Hz to 20 kHz           |              |

| V <sub>IH</sub>                                                                      | 2.4                       | V            |

| V <sub>IL</sub>                                                                      | 0.8                       | V            |

| External Load Impedance<br>(Line 0)                                                  | 10                        | kΩ           |

| External Load Impedance<br>(Line 1)                                                  | 48                        | Ω            |

| External Load Capacitance<br>(Line 0, 1)                                             | 100                       | pF           |

DAC Input Conditions 0 dB Attenuation Full-Scale Digital Inputs 16-Bit Linear Mode OLB = 1 ADC Input Conditions 0 dB PGA Gain -3.0 dB Relative to Full Scale Line Input 16-Bit Linear Mode

All tests are performed on all ADC and DAC channels.

## ANALOG INPUT

|                                     | Min   | Тур   | Max   | Unit  |

|-------------------------------------|-------|-------|-------|-------|

| Input Voltage*                      |       |       |       |       |

| (RMS Values Assume Sine Wave Input) |       |       |       |       |

| Line and Mic with 0 dB Gain         | 0 94  | 0.99  | 1.04  | V rms |

|                                     | 2.66  | 2.80  | 2.94  | V p-p |

| Mic with 20 dB Gain                 | 0.094 | 0.099 | 0.104 | V rms |

|                                     | 0.266 | 0.280 | 0.294 | V p-p |

| Input Capacitance                   |       |       | 15    | pF    |

\*Accounts for Sum of Worst Case Reference Errors and Worst Case Gain Errors.

## PROGRAMMABLE GAIN AMPLIFIER-ADC

|                                                                                    | Min          | Тур | Max           | Unit     |

|------------------------------------------------------------------------------------|--------------|-----|---------------|----------|

| Step Size (0 dB to 22.5 dB)<br>(All Steps Tested, -30 dB Input)<br>PGA Gain Range* | 1.3          | 1.5 | 1.7           | dB       |

| Line and Mic with 0 dB Gain<br>Mic with 20 dB Gain                                 | -0.2<br>19.8 |     | +22.7<br>42.7 | dB<br>dB |

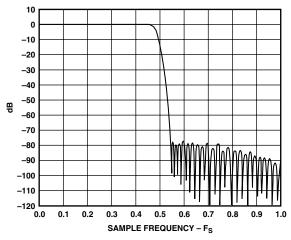

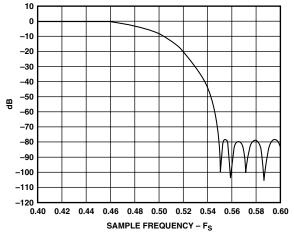

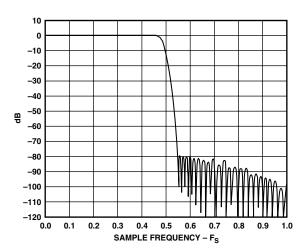

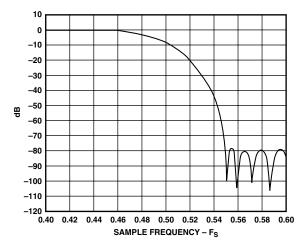

## DIGITAL DECIMATION AND INTERPOLATION FILTERS\*

|                                     | Min                      | Max                 | Unit |

|-------------------------------------|--------------------------|---------------------|------|

| Passband                            | 0                        | $0.45 \times F_{S}$ | Hz   |

| Passband Ripple                     |                          | $\pm 0.1$           | dB   |

| Transition Band                     | $0.45 \times F_{S}$      | $0.55 \times F_S$   | Hz   |

| Stopband                            | $\geq 0.55 \times F_{S}$ | _                   | Hz   |

| Stopband Rejection                  | 74                       |                     | dB   |

| Group Delay                         |                          | 30/F <sub>8</sub>   |      |

| Group Delay Variation Over Passband |                          | 0.0                 | μs   |

## ANALOG-TO-DIGITAL CONVERTERS

|                                                                                                                                                                                         | Min      | Тур                          | Max                          | Unit               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------|------------------------------|--------------------|

| Resolution*                                                                                                                                                                             |          | 16                           |                              | Bits               |

| ADC Dynamic Range, A-Weighted<br>Line and Mic with 0 dB Gain (-60 dB Input,<br>THD+N Referenced to Full Scale)<br>Mic with 20 dB Gain (-60 dB Input,<br>THD+N Referenced to Full Scale) | 74<br>72 | 83<br>74                     |                              | dB<br>dB           |

| ADC THD+N, (Referenced to Full Scale)<br>Line and Mic with 0 dB Gain<br>Mic with 20 dB Gain                                                                                             |          | 0.013<br>-78<br>0.032<br>-70 | 0.020<br>-72<br>0.056<br>-65 | %<br>dB<br>%<br>dB |

| ADC Crosstalk<br>Line to Line (Input L, Ground R,<br>Read R; Input R, Ground L, Read L)<br>Line to Mic (Input LINL & R,<br>Ground and Select MINL & R,<br>Read Both Channels)           |          |                              | -80<br>-60                   | dB<br>dB           |

| Gain Error (Full-Scale Span Relative to Nominal)                                                                                                                                        |          |                              | 0.75                         | dB                 |

| ADC Interchannel Gain Mismatch (Line and Mic)<br>(Difference of Gain Errors)                                                                                                            |          |                              | 0.3                          | dB                 |

#### DIGITAL-TO-ANALOG CONVERTERS

|                                                                                                                      | Min | Тур                                            | Max                                                                         | Unit                          |

|----------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------|

| Resolution*                                                                                                          |     | 16                                             |                                                                             | Bits                          |

| DAC Dynamic Range<br>(-60 dB Input, THD+N Referenced to Full Scale)                                                  | 80  | 86                                             |                                                                             | dB                            |

| DAC THD+N (Referenced to Full Scale)<br>Line 0 and 1 (10 kΩ Load)<br>Line 1 (48 Ω Load)<br>Mono Speaker (48 Ω Load)  |     | $0.010 \\ -80 \\ 0.022 \\ -73 \\ 0.045 \\ -67$ | $\begin{array}{c} 0.020 \\ -74 \\ 0.100 \\ -60 \\ 0.100 \\ -60 \end{array}$ | %<br>dB<br>%<br>dB<br>%<br>dB |

| DAC Crosstalk (Input L, Zero R, Measure<br>LOUT0R and 1R; Input R, Zero L,<br>Measure LOUT0L and 1L)                 |     |                                                | -80                                                                         | dB                            |

| Gain Error (Full-Scale Span Relative to Nominal)                                                                     |     |                                                | 0.75                                                                        | dB                            |

| DAC Interchannel Gain Mismatch (Line 0 and 1)<br>(Difference of Gain Errors)                                         |     |                                                | 0.3                                                                         | dB                            |

| Total Out-of-Band Energy*<br>(Measured from $0.55 \times F_S$ to 100 kHz)                                            |     |                                                | -60                                                                         | dB                            |

| Audible Out-of-Band Energy*<br>(Measured from 0.55 F <sub>s</sub> to 22 kHz,<br>All Selectable Sampling Frequencies) |     |                                                | -72                                                                         | dB                            |

\*Guaranteed, not tested.

## MONITOR MIX ATTENUATOR

|                                   | Min | Тур | Max | Unit |

|-----------------------------------|-----|-----|-----|------|

| Step Size (0.0 dB to -60 dB)*     | 1.3 | 1.5 | 1.7 | dB   |

| Step Size (-61.5 dB to -94.5 dB)* | 1.0 | 1.5 | 2.0 | dB   |

| Output Attenuation*               | -95 |     | 0.2 | dB   |

## DAC ATTENUATOR

|                                                                                           | Min        | Тур | Max        | Unit     |

|-------------------------------------------------------------------------------------------|------------|-----|------------|----------|

| Step Size (0.0 dB to -60 dB)<br>(Tested at Steps -1.5 dB, -19.5 dB,<br>-39 dB and -60 dB) | 1.3        | 1.5 | 1.7        | dB       |

| Step Size (-61.5 dB to -94.5 dB)*<br>Output Attenuation*                                  | 1.0<br>-95 | 1.5 | 2.0<br>0.2 | dB<br>dB |

## SYSTEM SPECIFICATIONS

|                            | Min  | Тур | Max       | Unit    |

|----------------------------|------|-----|-----------|---------|

| System Frequency Response* | -0.5 |     | +0.2      | dB      |

| (Line In to Line Out,      |      |     |           |         |

| 0 to $0.45 \times F_s$ )   |      |     |           |         |

| Differential Nonlinearity* |      |     | $\pm 0.9$ | LSB     |

| Phase Linearity Deviation* |      |     | 5         | Degrees |

## ANALOG OUTPUT

|                                                       | Min  | Тур   | Max  | Unit  |

|-------------------------------------------------------|------|-------|------|-------|

| Full-Scale Output Voltage (Line 0 & 1)                |      | 0.707 |      | V rms |

| [OLB = 1]                                             | 1.85 | 2.0   | 2.1  | V p-p |

| Full-Scale Output Voltage (Line 0)                    |      | 1.0   |      | V rms |

| [OLB = 0]                                             |      | 2.8   |      | V p-p |

| Full-Scale Output Voltage (Line 1)<br>[OLB = 0]       |      | 4.0   |      | V p-p |

| Full-Scale Output Voltage (Mono Speaker)<br>[OLB = 1] |      | 4.0   |      | V p-p |

| Full-Scale Output Voltage (Mono Speaker)<br>[OLB = 0] |      | 8.0   |      | V p-p |

| CMOUT Voltage (No Load)                               | 1.80 | 2.25  | 2.50 | V     |

| CMOUT Current Drive*                                  |      | 100   |      | μA    |

| CMOUT Output Impedance                                |      | 4     |      | kΩ    |

| Mute Attenuation of 0 dB                              |      |       | -80  | dB    |

| Fundamental* (LINE 0, 1, and MONO)                    |      |       |      |       |

## STATIC DIGITAL SPECIFICATIONS

|                                                                    | Min  | Max               | Unit |

|--------------------------------------------------------------------|------|-------------------|------|

| High Level Input Voltage (V <sub>IH</sub> )                        |      |                   |      |

| Digital Inputs                                                     | 2.4  | $(V_{DD}+) + 0.3$ | V    |

| XTAL1/2I                                                           | 2.4  | $(V_{DD}+) + 0.3$ | V    |

| Low Level Input Voltage $(V_{II})$                                 | -0.3 | +0.8              | V    |

| High Level Output Voltage ( $V_{OH}$ ) at $I_{OH} = -2 \text{ mA}$ | 2.4  |                   | V    |

| Low Level Output Voltage ( $V_{OL}$ ) at $I_{OL} = 2 \text{ mA}$   |      | 0.4               | V    |

| Input Leakage Current                                              | -10  | +10               | μΑ   |

| (GO/NOGO Tested)                                                   |      |                   |      |

| Output Leakage Current<br>(GO/NOGO Tested)                         | -10  | +10               | μΑ   |

\*Guaranteed, not tested.

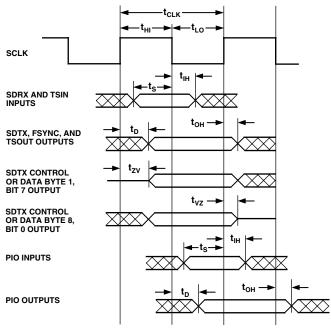

## DIGITAL TIMING PARAMETERS (Guaranteed over 4.75 V to 5.25 V, 0°C to 70°C)

|                                         | Min | Тур                            | Max  | Unit |

|-----------------------------------------|-----|--------------------------------|------|------|

| SCLK Period (t <sub>CLK</sub> )         |     |                                |      |      |

| Slave Mode, $MS = 0$                    | 80  |                                |      | ns   |

| Master Mode, $MS = 1^*$                 |     | $1/(F_S \times Bits per Frame$ | e)   | s    |

| SCLK HI (t <sub>HI</sub> )*             |     |                                |      |      |

| Slave Mode, $MS = 0$                    | 25  |                                |      | ns   |

| SCLK LO (t <sub>LO</sub> )*             |     |                                |      |      |

| Slave Mode, $MS = 0$                    | 25  |                                |      | ns   |

| CLKIN Frequency                         |     |                                | 13.5 | MHz  |

| CLKIN HI                                | 30  |                                |      | ns   |

| CLKIN LO                                | 30  |                                |      | ns   |

| Crystals Frequency                      |     |                                | 27   | MHz  |

| Input Setup Time (t <sub>s</sub> )      | 15  |                                |      | ns   |

| Input Hold Time (t <sub>IH</sub> )      | 10  |                                |      | ns   |

| Output Delay (t <sub>D</sub> )          |     |                                | 25   | ns   |

| Output Hold Time (t <sub>OH</sub> )     | 0   |                                |      | ns   |

| Output Hi-Z to Valid (t <sub>ZV</sub> ) | 15  |                                |      | ns   |

| Output Valid to Hi-Z (t <sub>VZ</sub> ) |     |                                | 20   | ns   |

| Power Up RESET LO Time                  | 50  |                                |      | ms   |

| Operating RESET LO Time                 | 100 |                                |      | ns   |

## **POWER SUPPLY**

|                                                                  | Min  | Тур | Max  | Unit |

|------------------------------------------------------------------|------|-----|------|------|

| Power Supply Voltage Range*                                      | 4.75 |     | 5.25 | V    |

| -Digital and Analog<br>Power Supply Current—Operating            |      | 100 | 130  | mA   |

| (50% I <sub>VDD</sub> , 50% I <sub>VCC</sub> , Unloaded Outputs) |      | 100 | 150  | шл   |

| Power Supply Current—Power Down                                  |      | 20  | 200  | μΑ   |

| Power Supply Rejection (@ 1 kHz)*                                | 40   |     |      | dB   |

| (At Both Analog and Digital                                      |      |     |      |      |

| Supply Pins, Both ADCs and DACs)                                 |      |     |      |      |

## **CLOCK SPECIFICATIONS\***

|                                 | Min    | Max      | Unit |

|---------------------------------|--------|----------|------|

| Input Clock Frequency, Crystals |        | 27       | MHz  |

| Clock Duty Cycle Tolerance      |        | $\pm 10$ | %    |

| Sample Rate (F <sub>S</sub> )   | 5.5125 | 50       | kHz  |

\*Guaranteed, not tested.

Specifications subject to change without notice.

### ABSOLUTE MAXIMUM RATINGS\*

|                                     | Min  | Max               | Unit |

|-------------------------------------|------|-------------------|------|

| Power Supplies                      |      |                   |      |

| Digital (V <sub>DD</sub> )          | -0.3 | +6.0              | V    |

| Analog (V <sub>CC</sub> )           | -0.3 | +6.0              | v    |

| Input Current                       |      |                   |      |

| (Except Supply Pins and MOUT,       |      | $\pm 10.0$        | mA   |

| MOUTR, LOUT1R, LOUT1L,              |      |                   |      |

| LOUT1C)                             |      |                   |      |

| Analog Input Voltage (Signal Pins)  | -0.3 | $(V_{CC}+) + 0.3$ | v    |

| Digital Input Voltage (Signal Pins) | -0.3 | $(V_{DD}+) + 0.3$ | V    |

| Ambient Temperature (Operating)     | 0    | 70                | °C   |

| Storage Temperature                 | -65  | +150              | °C   |

| ESD Tolerance (Human Body           | 500  |                   | v    |

| Model per Method 3015.2             |      |                   |      |

| of MIL-STD-883B)                    |      |                   |      |

\*Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**WARNING**: CMOS device. May be susceptible to high-voltage transient-induced latchup.

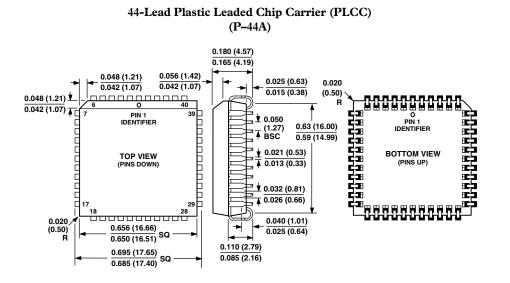

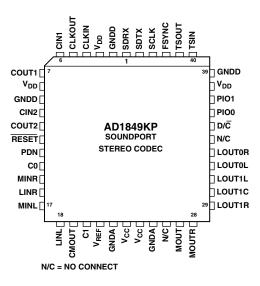

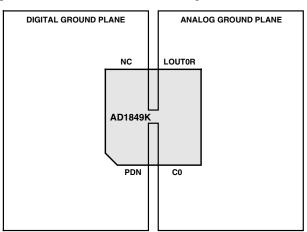

#### PIN CONFIGURATION 44-Lead Plastic Leaded Chip Carrier

### **ORDERING GUIDE**

| Model    | Temperature | Package      | Package |  |

|----------|-------------|--------------|---------|--|

|          | Range       | Description  | Option  |  |

| AD1849KP | 0°C to 70°C | 44-Lead PLCC | P-44A   |  |

#### **CAUTION**\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD1849K features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

## PIN FUNCTION DESCRIPTIONS

| Pin Name         | PLCC | I/O | Description                                     |  |  |

|------------------|------|-----|-------------------------------------------------|--|--|

| SDRX             | 1    | I   | Receive Serial Data Pin                         |  |  |

| SDTX             | 44   | 0   | Transmit Serial Data Pin                        |  |  |

| SCLK             | 43   | I/O | Bidirectional Serial Bit Clock                  |  |  |

| FSYNC            | 42   | 0   | Frame Sync Output Signal                        |  |  |

| TSOUT            | 41   | 0   | Chaining Word Output                            |  |  |

| TSIN             | 40   | I   | Chaining Word Input                             |  |  |

| $D/\overline{C}$ | 35   | I   | Data/Control Select Input                       |  |  |

| CIN1             | 6    | I   | Crystal 1 Input                                 |  |  |

| COUT1            | 7    | 0   | Crystal 1 Output                                |  |  |

| CIN2             | 10   | I   | Crystal 2 Input                                 |  |  |

| COUT2            | 11   | 0   | Crystal 2 Output                                |  |  |

| CLKIN            | 4    | I   | External Sample Clock Input $(256 \times F_s)$  |  |  |

| CLKOUT           | 5    | 0   | External Sample Clock Output $(256 \times F_s)$ |  |  |

| PDN              | 13   | I   | Power Down Input (Active HI)                    |  |  |

| RESET            | 12   | I   | Reset Input (Active LO)                         |  |  |

| PIO1             | 37   | I/O | Parallel Input/Output Bit 1                     |  |  |

| PIO0             | 36   | I/O | Parallel Input/Output Bit 0                     |  |  |

## **Analog Signals**

**Digital Signals**

| Pin Name         | PLCC | I/O | Description                                                                               |

|------------------|------|-----|-------------------------------------------------------------------------------------------|

| LINL             | 18   | I   | Left Channel Line Input                                                                   |

| LINR             | 16   | I   | Right Channel Line Input                                                                  |

| MINL             | 17   | I   | Left Channel Microphone Input (-20 dB from Line Level if MB = 0 or Line Level if MB = 1)  |

| MINR             | 15   | Ι   | Right Channel Microphone Input (-20 dB from Line Level if MB = 0 or Line Level if MB = 1) |

| LOUT0L           | 32   | 0   | Left Channel Line Output 0                                                                |

| LOUTOR           | 33   | 0   | Right Channel Line Output 0                                                               |

| LOUT1L           | 31   | 0   | Left Channel Line Output 1                                                                |

| LOUT1R           | 29   | 0   | Right Channel Line Output 1                                                               |

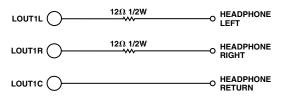

| LOUT1C           | 30   | Ι   | Common Return Path for Large Current from External Headphones                             |

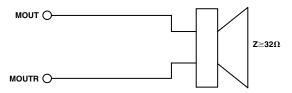

| MOUT             | 27   | 0   | Mono Speaker Output                                                                       |

| MOUTR            | 28   | Ι   | Mono Speaker Output Return                                                                |

| C0               | 14   | 0   | External 1.0 µF Capacitor (±10%) Connection                                               |

| C1               | 20   | 0   | External 1.0 µF Capacitor (±10%) Connection                                               |

| N/C              | 26   |     | No Connect (Do Not Connect)                                                               |

| N/C              | 34   |     | No Connect (Do Not Connect)                                                               |

| V <sub>REF</sub> | 21   | 0   | Voltage Reference (Connect to Bypass Capacitor)                                           |

| CMOUT            | 19   | 0   | Common Mode Reference Datum Output (Nominally 2.25 V)                                     |

## **Power Supplies**

| Pin Name        | PLCC      | I/O | Description                  |  |  |

|-----------------|-----------|-----|------------------------------|--|--|

| V <sub>CC</sub> | 23 and 24 | Ι   | Analog Supply Voltage (5 V)  |  |  |

| GNDA            | 22 and 25 | Ι   | Analog Ground                |  |  |

| V <sub>DD</sub> | 3, 8, 38  | Ι   | Digital Supply Voltage (5 V) |  |  |

| GNDD            | 2, 9, 39  | Ι   | Digital Ground               |  |  |

### FUNCTIONAL DESCRIPTION

This section overviews the functionality of the AD1849K and is intended as a general introduction to the capabilities of the device. As much as possible, detailed reference information has been placed in "Control Registers" and other sections. The user is not expected to refer repeatedly to this section.

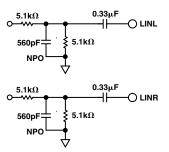

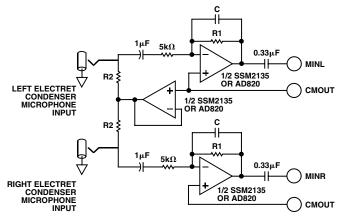

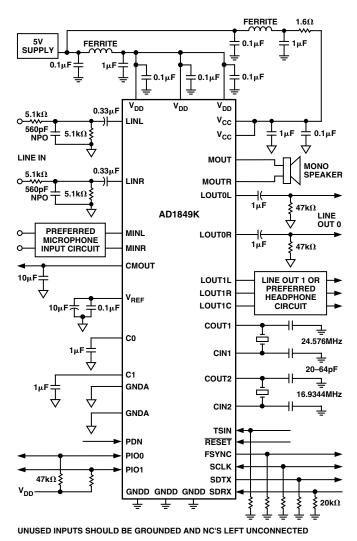

### **Analog Inputs**

The AD1849K SoundPort Stereo Codec accepts stereo line-level and mic-level inputs. These analog stereo signals are multiplexed to the internal programmable gain amplifier (PGA) stage. The mic inputs can be amplified by 20 dB prior to the PGA to compensate for the voltage swing difference between line levels and typical condenser microphones. The mic inputs can bypass the 20 dB fixed gain block and go straight to the input multiplexer, which often results in an improved system signal-to-noise ratio.

The PGA following the input multiplexer allows independent selectable gains for each channel from 0 to 22.5 dB in 1.5 dB steps. The Codec can operate either in a global stereo mode or in a global mono mode with left-channel inputs appearing at both channel outputs.

## Analog-to-Digital Datapath

The AD1849K  $\Sigma\Delta$  ADCs incorporate a proprietary fourth-order modulator. A single pole of passive filtering is all that is required for antialiasing the analog input because of the ADC's high 64 times oversampling ratio. The ADCs include linear-phase digital decimation filters that low-pass filter the input to  $0.45 \times F_S$  ("F<sub>S</sub>" is the word rate or "sampling frequency"). ADC input overrange conditions will cause a sticky bit to be set that can be read.

#### **Digital-to-Analog Datapath**

The  $\Sigma\Delta$  DACs are preceded by a programmable attenuator and a low-pass digital interpolation filter. The attenuator allows independent control of each DAC channel from 0 dB to -94.5 dB in 1.5 dB steps plus full digital mute. The anti-imaging interpolation filter oversamples by 64 and digitally filters the higher frequency images. The DACs'  $\Sigma\Delta$  noise shapers also oversample by 64 and convert the signal to a single-bit stream. The DAC outputs are then filtered in the analog domain by a combination of switched-capacitor and continuous-time filters. They remove the very high frequency components of the DAC bitstream output, including both images at the oversampling rate and shaped quantization noise. No external components are required. Phase linearity at the analog output is achieved by internally compensating for the group delay variation of the analog output filters.

Attenuation settings are specified by control bits in the data stream. Changes in DAC output level take effect only on zero crossings of the digital signal, thereby eliminating "zipper" noise. Each channel has its own independent zero-crossing detector and attenuator change control circuitry. A timer guarantees that requested volume changes will occur even in the absence of an input signal that changes sign. The time-out period is 10.7 milliseconds at a 48 kHz sampling rate and 64 milliseconds at an 8 kHz sampling rate (Time-out [ms]  $\approx$  512/ Sampling Rate [kHz]).

### **Monitor Mix**

A monitor mix is supported that digitally mixes a portion of the digitized analog input with the analog output (prior to digitization). The digital output from the ADCs going out of the serial data port is unaffected by the monitor mix. Along the monitor mix datapath, the 16-bit linear output from the ADCs is attenuated by an amount specified with control bits. Both channels of the monitor data are attenuated by the same amount. (Note that internally the AD1849K always works with 16-bit PCM linear data, digital mixing included; format conversions take place at the input and output.)

Sixteen steps of -6 dB attenuation are supported to -94.5 dB. A "0" implies no attenuation, while a "14" implies 84 dB of attenuation. Specifying full scale "15" completely mutes the monitor datapath, preventing any mixing of the analog input with the digital input. Note that the level of the mixed output signal is also a function of the input PGA settings since they affect the ADCs' output.

The attenuated monitor data is digitally summed with the DAC input data prior to the DACs' datapath attenuators. Because both stereo signals are mixed before the output attenuators, mix data is attenuated a second time by the DACs' datapath attenuators. The digital sum of digital mix data and DAC input data is clipped at plus or minus full scale and does not wrap around.

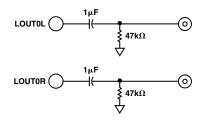

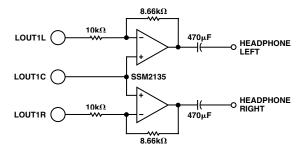

### **Analog Outputs**

One stereo line-level output, one stereo headphone output, and one monaural (mono) speaker output are available at external pins. Each of these outputs can be independently muted. Muting either the line-level stereo output or the headphone stereo output mutes both left and right channels of that output. When muted, the outputs will settle to a dc value near CMOUT, the midscale reference voltage. The mono speaker output is differential. The chip can operate either in a global stereo mode or in a global mono mode with left channel inputs appearing at both outputs.

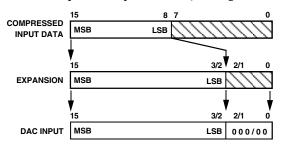

#### **Digital Data Types**

The AD1849K supports four global data types: 16-bit twoscomplement linear PCM, 8-bit unsigned linear PCM, 8-bit companded µ-law, and 8-bit companded A-law, as specified by control register bits. Data in all four formats is always transferred MSB first. Sixteen-bit linear data output from the ADCs and input to the DACs is in twos-complement format. Eight-bit data is always left-justified in 16-bit fields; in other words, the MSBs of all data types are always aligned; in yet other words, full-scale representations in all three formats correspond to equivalent full-scale signals. The eight least-significant bit positions of 8-bit linear and companded data in 16-bit fields are ignored on input and zeroed on output.

The 16-bit PCM data format is capable of representing 96 dB of dynamic range. Eight-bit PCM can represent 48 dB of dynamic range. Companded  $\mu$ -law and A-law data formats use nonlinear coding with less precision for large-amplitude signals. The loss of precision is compensated for by an increase in dynamic range to 64 dB and 72 dB, respectively.

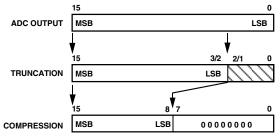

On input, 8-bit companded data is expanded to an internal linear representation, according to whether  $\mu$ -law or A-law was specified in the Codec's internal registers. Note that when  $\mu$ -law compressed data is expanded to a linear format, it requires 14 bits. A-law data expanded requires 13 bits, see Figure 1.

Figure 1. A-Law or µ-Law Expansion

When 8-bit companding is specified, the ADCs' linear output is compressed to the format specified prior to output. See Figure 2.

Note that all format conversions take place at input or output. Internally, the AD1849K always uses 16-bit linear PCM representations to maintain maximum precision.

Figure 2. A-Law or µ-Law Compression

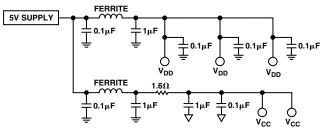

## Power Supplies and Voltage Reference

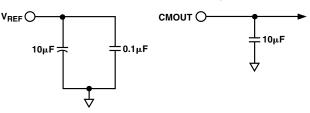

The AD1849K operates from 5 V power supplies. Independent analog and digital supplies are recommended for optimal performance, though excellent results can be obtained in single supply systems. A voltage reference is included on the Codec and its 2.25 V buffered output is available on an external pin (CMOUT). The CMOUT output can be used for biasing op amps used in dc coupling. The internal reference is externally bypassed to analog ground at the  $V_{REF}$  pin. Note that  $V_{REF}$  should only be connected to its bypass capacitors.

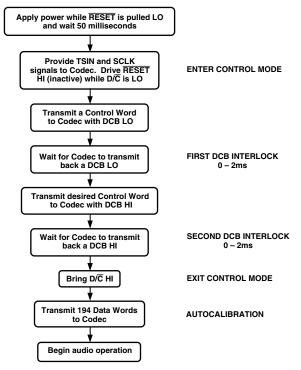

## Autocalibration

The AD1849K supports an autocalibration sequence to eliminate DAC and ADC offsets. The autocalibration sequence is initiated in the transition from Control Mode to Data Mode, regardless of the state of the AC bit. The user should specify that analog outputs be muted to prevent undesired outputs. Monitor mix will be automatically disabled by the Codec.

During the autocalibration sequence, the serial data output from the ADCs is meaningless and the ADI bit is asserted. Serial data inputs to the DACs are ignored. Even if the user specified the muting of all analog outputs, near the end of the autocalibration sequence, dc analog outputs very close to CMOUT will be produced at the line outputs and mono speaker output.

An autocalibration sequence is also performed when the AD1849K leaves the reset state (i.e.,  $\overrightarrow{\text{RESET}}$  goes HI). The  $\overrightarrow{\text{RESET}}$  pin should be held LO for 50 ms after power up or after leaving power-down mode to delay the onset of the autocalibration sequence until after the voltage reference has settled.

## Loopback

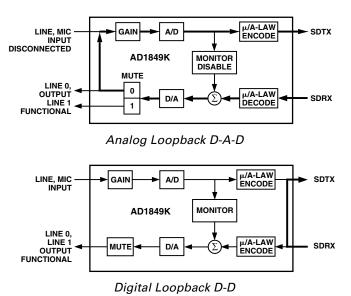

Digital and analog loopback modes are supported for device and system testing. The monitor mix datapath is always available for loopback test purposes. Additional loopback tests are enabled by setting the ENL bit (Control Word Bit 33) to a "1."

Analog loopback mode D-A-D is enabled by setting the ADL bit (Control Word Bit 32) to a "1" when ENL is a "1." In this mode, the DACs' analog outputs are re-input to the PGAs prior to the ADCs, allowing digital inputs to be compared to digital outputs. The monitor mix will be automatically disabled by the Codec during D-A-D loopback. The analog outputs can be individually attenuated, and the analog inputs are internally disconnected. Note that muting the line 0 output mutes the looped-back signal in this mode.

Digital loopback mode D-D is enabled by resetting the ADL bit (Control Word Bit 32) to a "0" when ENL is a "1." In this mode, the control and data bit pattern presented on the SDRX pin is echoed on the SDTX pin with a two frame delay, allowing the host controller to verify the integrity of the serial interface starting on the third frame after D-D loopback is enabled. During digital loopback mode, the output DACs are operational.

The loopback modes are shown graphically in Figure 3.

Figure 3. Loopback Modes

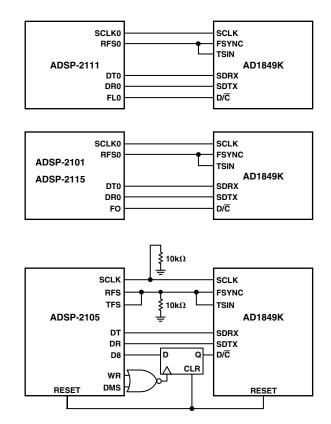

#### **Clocks and Sample Rates**

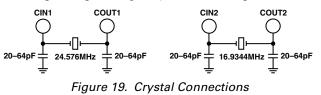

The AD1849K can operate from external crystals, from a  $256 \times$ F<sub>s</sub> input clock, from an input clock with a programmable divide factor, or from the serial port's bit clock (at  $256 \times F_S$ ), selected under software control. Two crystal inputs are provided to generate a wide range of sample rates. The oscillators for these crystals are on the AD1849K, as is a multiplexer for selecting between them. They can be overdriven with external clocks by the user, if so desired. The recommended crystal frequencies are 16.9344 MHz and 24.576 MHz. From them the following sample rates can be internally generated: 5.5125, 6.615, 8, 9.6, 11.025, 16, 18.9, 22.05, 27.42857, 32, 33.075, 37.8, 44.1, 48 kHz. Regardless of clock input source, a clock output of  $256 \times F_8$  is generated (with some skew). If an external input clock or the serial port's bit clocks are selected to drive the AD1849K's internal operation, they should be low jitter clocks. If no external clock will be used, Analog Devices recommends tying the clock input pin (CLKIN) to ground. If either external crystal is not used, Analog Devices recommends tying its input (CIN1 and/or CIN2) to ground.

## **CONTROL REGISTERS**

The AD1849K SoundPort Stereo Codec accepts control information through its serial port when in Control Mode. Some control information is also embedded in the data stream when in Data Mode. (See Figure 8.) Control bits can also be read back for system verification. Operation of the AD1849K is determined by the state of these control bits. The 64-bit serial Control Mode and Data Mode control registers have been arbitrarily broken down into bytes for ease of description. All control bits initialize to default states after RESET or Power Down. Those control bits that cannot be changed in Control Mode are initialized to defaults on the transition from Data Mode to Control Mode. See below for a definition of these defaults.

### **Control Mode Control Registers**

#### Control Byte 1, Status Register

| Data 7 | Data 6 | Data 5 | Data 4 | Data 3 | Data 2 | Data 1 | Data 0 | _ |

|--------|--------|--------|--------|--------|--------|--------|--------|---|

| 0      | 0      | 1      | MB     | OLB    | DCB    | 0      | AC     |   |

| 63     | 62     | 61     | 60     | 59     | 58     | 57     | 56     |   |

#### MB Mic bypass:

| Mic inputs applied to : | 20 dB fixed gain block. |

|-------------------------|-------------------------|

|-------------------------|-------------------------|

Mic inputs bypass 20 dB fixed gain block.

#### 1 Mic OLB Output level bit:

0

Full-scale line 0 output is 2.8 V p-p (1 V rms). Full-scale line 1 output is 4.0 V p-p. Full-scale mono speaker output is 8.0 V p-p.

Full-scale line 0 output is 2.0 V p-p. Full-scale line 1 output is 2.0 V p-p.

Full-scale mono speaker output is 4.0 V p-p.

DCB Data/control bit. Used for handshaking in data/control transitions. See "DCB Handshake Protocol."

#### AC Autocalibration.

Autocalibration will always occur on the Control-to-Data mode transition. The AC bit is ignored. Autocalibration requires an interval of 194 frames. Offsets for all channels of ADC and DAC are zeroed. The user should specify that analog outputs are muted to prevent undesired outputs, i.e., OM0 = "0," OM1 = "0," and SM = "0." Monitor mix will be automatically disabled by the Codec.

### Control Byte 2, Data Format Register

|         | Data 7           | Data 6            | Data 5                              | Data 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Data 3                                | Data 2                          | Data 1           | Data 0                                                        |

|---------|------------------|-------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------|------------------|---------------------------------------------------------------|

|         | 0                | 0                 | DFR2                                | DFR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DFR0                                  | ST                              | DF1              | DF0                                                           |

|         | 55               | 54                | 53                                  | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51                                    | 50                              | 49               | 48                                                            |

| DFR2:0  | ) Data co        | onversion frequer | ncy $(F_S)$ select t                | in kHz:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |                                 |                  |                                                               |

|         | DFR              | Divide Factor     | •                                   | ХТА                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | L1 (24.576 MH                         | Hz)                             | XTAL2 (16.9      | 344 MHz)                                                      |

|         | 0                | 3072              |                                     | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |                                 | 5.5125           |                                                               |

|         | 1                | 1536              |                                     | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                                 | 11.025           |                                                               |

|         | 2                | 896               |                                     | 27.42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2857                                  |                                 | 18.9             |                                                               |

|         | 3                | 768               |                                     | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                                 | 22.05            |                                                               |

|         | 4                | 448               |                                     | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       |                                 | 37.8             |                                                               |

|         | 5                | 384               |                                     | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       |                                 | 44.1             |                                                               |

|         | 6                | 512               |                                     | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                                 | 33.075           |                                                               |

|         | 7                | 2560              |                                     | 9.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       |                                 | 6.615            |                                                               |

|         | externa<br>(COUT | l clock source is | used, it should<br>hould be left ur | be applied to the tothe termination of the termination of terminatioo | ne crystal input<br>le external clock | pin (CIN1 or 0<br>source need n | CIN2), and the   | stal input pins. If<br>crystal output pin<br>commended crysta |

| ST      |                  | stereo mode. Bot  |                                     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |                                 |                  |                                                               |

|         |                  |                   | left analog input                   | appears at both                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | n ADC outputs.                        | The left digital                | input appears at | t both DAC outpu                                              |