- Combines Decoder and 3-Bit Address Latch

- Incorporates 2 Enable Inputs to Simplify Cascading

- Low Power Dissipation . . . 65 mW Typ

#### description

The 'LS137 is a three-line to eight-line decoder/demultiplexer with latches on the three address inputs. When the latch-enable input (\$\overline{GL}\$) is low, the 'LS137 acts as a decoder/demultiplexer. When \$\overline{GL}\$ goes from low to high, the address present at the select inputs (A,B, and C) is stored in the latches. Further address changes are ignored as long as \$\overline{GL}\$ remains high. The output enable controls, \$G1\$ and \$\overline{G2}\$, control the state of the outputs independently of the select or latchenable inputs. All of the outputs are high unless \$G1\$ is high and \$\overline{G2}\$ is low. The 'LS137 is ideally suited for implementing glitch-free decoders in strobed (stored-address) applications in bus-oriented systems.

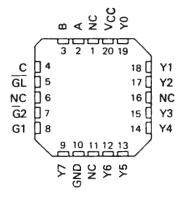

# SN54LS137 . . .FK PACKAGE (TOP VIEW)

NC - No internal connection

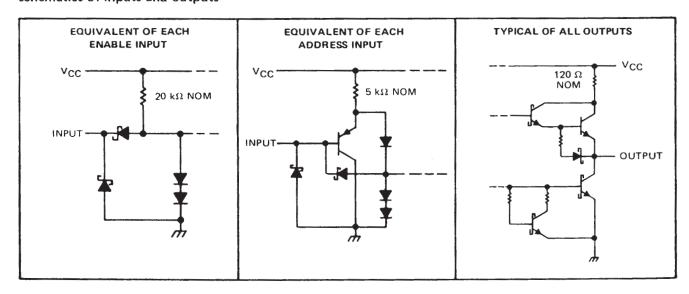

#### schematics of inputs and outputs

#### SDLS132 – JUNE 1978 – REVISED MARCH 1988

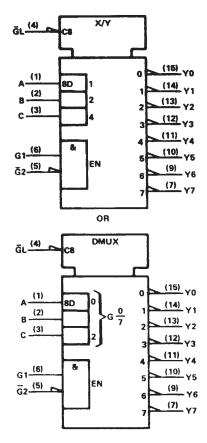

## logic symbols†

<sup>†</sup>These symbols are in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for D, J, N, and W packages.

#### **FUNCTION TABLE**

| INPUTS |               |    |   |   | OUTPUTS |                           |           |           |           |           |     |       |           |  |  |  |

|--------|---------------|----|---|---|---------|---------------------------|-----------|-----------|-----------|-----------|-----|-------|-----------|--|--|--|

| EN     | ENABLE SELECT |    |   |   |         |                           |           |           |           |           |     |       |           |  |  |  |

| GL     | G1            | G2 | C | В | A       | YO                        | <b>Y1</b> | <b>Y2</b> | <b>Y3</b> | <b>Y4</b> | Y5  | Y6    | <b>Y7</b> |  |  |  |

| X      | ×             | Н  | Х | х | х       | Н                         | Н         | Н         | Н         | Н         | Н   | Н     | Н         |  |  |  |

| x      | L             | х  | × | X | X       | н                         | Н         | Н         | Н         | Н         | Н   | Н     | Н         |  |  |  |

| L      | Н             | L  | L | L | L       | L                         | Н         | Н         | Н         | Н         | Н   | Н     | Н         |  |  |  |

| L      | н             | L  | L | L | Н       | н                         | L         | Н         | Н         | Н         | Н   | н     | Н         |  |  |  |

| L      | н             | L  | Ł | Н | L       | Н                         | Н         | L         | Н         | Н         | Н   | Н     | Н         |  |  |  |

| L      | Н             | L  | L | Н | Н       | н                         | Н         | Н         | L         | Н         | Н   | Н     | Н         |  |  |  |

| L      | Н             | L  | Н | L | L       | Н                         | Н         | Н         | Н         | L         | Н   | Н     | Н         |  |  |  |

| L      | Н             | L  | н | L | Н       | н                         | Н         | Н         | Н         | Н         | L   | Н     | Н         |  |  |  |

| L      | Н             | L  | н | н | L       | н                         | Н         | Н         | Н         | Н         | Н   | L     | Н         |  |  |  |

| L      | Н             | L  | н | Н | Н       | н                         | Н         | Н         | Н         | Н         | Н   | Н     | L         |  |  |  |

|        |               |    |   |   | · ·     | Ou                        | tput      | corr      | espo      | ndin      | to: | store | d         |  |  |  |

| Н      | Н             | L  | X | X | ×       | address, L; all others, H |           |           |           |           |     |       |           |  |  |  |

H = high level, L = low level, X = irrelevant

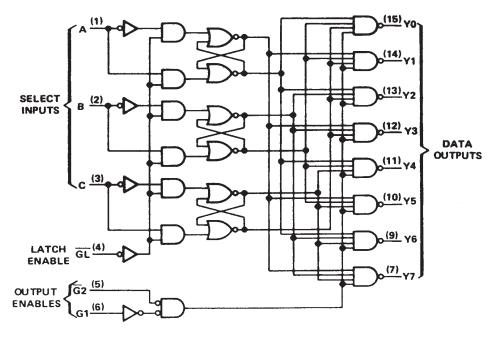

#### logic diagram (positive logic)

Pin numbers shown are for D, J, N, and W packages.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (See Note 1)                |  |   |  |  |  |   |  |  |  |          | 7 V     |

|-------------------------------------------------|--|---|--|--|--|---|--|--|--|----------|---------|

| Input voltage                                   |  |   |  |  |  |   |  |  |  |          | 7 V     |

| Operating free-air temperature range: SN54LS137 |  |   |  |  |  |   |  |  |  | –55°C to | o 125°C |

| SN74LS137                                       |  |   |  |  |  |   |  |  |  | . 0°C    | to 70°C |

| Storage temperature range                       |  | _ |  |  |  | _ |  |  |  | 65°C to  | o 150°C |

NOTE 1: Voltage values are with respect to network ground terminal.

# SN54LS137, SN74LS137 3-LINE TO 8-LINE DECODERS/DEMULTIPLEXERS WITH ADDRESS LATCHES

SDLS132 – JUNE 1978 – REVISED MARCH 1988

#### recommended operating conditions

|                                                   | S   | S                   |      |      |   |      |    |

|---------------------------------------------------|-----|---------------------|------|------|---|------|----|

|                                                   | MIN | NOM MAX MIN NOM MAX | MAX  | UNIT |   |      |    |

| Supply voltage, V <sub>CC</sub>                   | 4.5 | 5                   | 5.5  | 4.75 | 5 | 5.25 | ٧  |

| High-level output current, IOH                    |     |                     | -400 |      |   | -400 | μА |

| Low-level output current, IOL                     |     |                     | 4    |      |   | 8    | mA |

| Width of enabling pulse at GL, tw                 | 15  |                     |      | 15   |   |      | ns |

| Setup time at A, B, and C inputs, t <sub>su</sub> | 10  | ,                   |      | 10   |   |      | ns |

| Hold time at A, B, and C inputs, th               | 10  |                     |      | 10   |   |      | ns |

| Operating free-air temperature, TA                | -55 |                     | 125  | 0    |   | 70   | °C |

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                 |                                        |                                                                  | S                                                   | N54LS1                 | 37  | S                |      |     |      |      |            |

|-----------------|----------------------------------------|------------------------------------------------------------------|-----------------------------------------------------|------------------------|-----|------------------|------|-----|------|------|------------|

|                 | PARAMETER                              | TES                                                              | T CONDITIONS                                        |                        | MIN | TYP <sup>‡</sup> | MAX  | MIN | TYP‡ | MAX  | UNIT       |

| VIH             | High-level input voltage               |                                                                  |                                                     |                        | 2   |                  |      | 2   |      |      | V          |

| VIL             | Low-level input voltage                |                                                                  |                                                     |                        |     |                  | 0.7  |     |      | 8.0  | ٧          |

| VIK             | Input clamp voltage                    | V <sub>CC</sub> = MIN,                                           | I <sub>I</sub> = -18 mA                             |                        |     |                  | -1.5 |     |      | -1.5 | V          |

| Vон             | High-level output voltage              | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = V <sub>IL</sub> max, | V <sub>1H</sub> = 2 V,<br>I <sub>OH</sub> = -400 μA |                        | 2.5 | 3.5              |      | 2.7 | 3.5  |      | V          |

|                 |                                        | V <sub>CC</sub> = MIN,                                           | V <sub>IH</sub> = 2 V,                              | IOL = 4 mA             |     | 0.25             | 0.4  |     | 0.25 | 0.4  | V          |

| VOL             | Low-level output voltage               | VIL = VIL max                                                    |                                                     | 1 <sub>OL</sub> = 8 mA |     |                  |      |     | 0.35 | 0.5  | 1 <u> </u> |

| 11              | Input current at maximum input voltage | V <sub>CC</sub> = MAX,                                           | V <sub>I</sub> = 7 V                                |                        |     |                  | 0.1  |     |      | 0.1  | mA         |

| Чн              | High-level input current               | V <sub>CC</sub> = MAX,                                           | V <sub>1</sub> = 2.7 V                              |                        |     |                  | 20   |     |      | 20   | μА         |

|                 |                                        |                                                                  |                                                     | Enable                 |     |                  | -0.4 |     |      | -0.4 | ^          |

| HL              | Low-level input current                | V <sub>CC</sub> = MAX,                                           | V <sub>I</sub> = 0.4 V                              | A,B,C                  |     |                  | -0.2 |     |      | -0.2 | mA         |

| los             | Short-circuit output current §         | V <sub>CC</sub> = MAX                                            |                                                     |                        | -20 |                  | -100 | 20  |      | -100 | mA         |

| 1 <sub>CC</sub> | Supply current                         | V <sub>CC</sub> = MAX,                                           | See Note 2                                          |                        |     | 11               | 18   |     | 11   | 18   | mA         |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

NOTE 2: I<sub>CC</sub> is tested with all inputs grounded and all outputs open.

## switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ} \text{ C}$ , see note 3

| PARAMETER 1      | FROM<br>(INPUT) | TO<br>(OUTPUT) | LEVELS<br>OF DELAY | TEST<br>CONDITIONS      | MIN | TYP | MAX | UNIT         |

|------------------|-----------------|----------------|--------------------|-------------------------|-----|-----|-----|--------------|

| t <sub>PLH</sub> |                 | Y              | 2                  |                         |     | 11  | 17  | ns           |

| t <sub>PHL</sub> | A, B, C         | Υ .            | 4                  |                         |     | 25  | 38  | ] '''        |

| t <sub>PLH</sub> | 4.5.0           | Y              | 3                  |                         |     | 16  | 24  | ns           |

| t <sub>PHL</sub> | A, B, C         | Y              | 3                  |                         |     | 19  | 29  | <u>l '''</u> |

| ¹PLH             | F 50            | Υ              | 2                  | C <sub>L</sub> = 15 pF, |     | 13  | 21  | ns           |

| tPHL             | Enable G2       | , r            | 2                  | $R_L = 2 k\Omega$ ,     |     | 16  | 27  |              |

| tPLH             | 5 11 64         | V              | 3                  | See Note 3              |     | 14  | 21  | ns           |

| tPHL             | Enable G1       | Y              | 3                  |                         |     | 18  | 27  |              |

| <sup>t</sup> PLH | 5 11 5          | .,             | 3                  |                         |     | 18  | 27  | ns           |

| <sup>†</sup> PHL | Enable GL       | Y              | 4                  |                         |     | 25  | 38  | ] '''        |

$<sup>1</sup>_{tplH}$  = propagation delay time, low-to-high-level output.

NOTE 3: Load circuits and voltage waveforms are shown in Section 1.

$<sup>^{\</sup>ddagger}$ All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_{A} = 25^{\circ} \text{C}$ .

<sup>§</sup> Not more than one output should be shorted at a time, and duration of the short-circuit should not exceed one second.

tpHL = propagation delay time, high-to-low-level output.