- Digital Design Avoids Analog Compensation Errors

- Easily Cascadable for Higher Order Loops

- Useful Frequency from DC to:

50 MHz Typical (K Clock)

35 MHz Typical (I/D Clock)

#### description

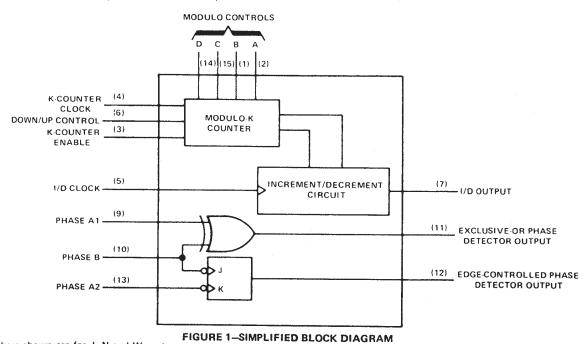

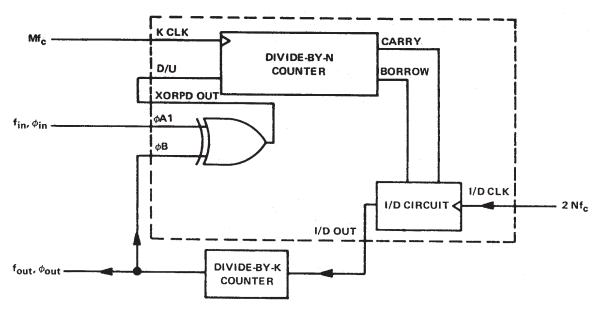

The SN54LS297 and SN74LS297 devices are designed to provide a simple, cost-effective solution to high-accuracy, digital, phase-locked-loop applications. These devices contain all the necessary circuits, with the exception of the divide-by-N counter, to build first order phase-locked loops as described in Figure 1.

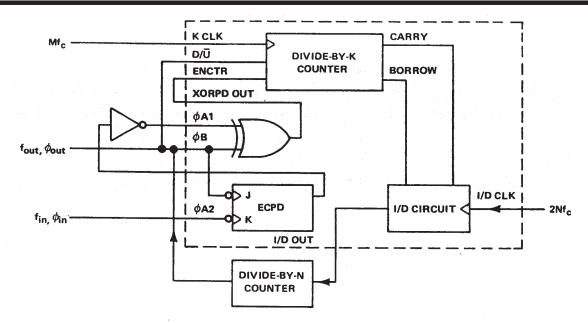

Both exclusive-OR (XORPD) and edge-controlled (ECPD) phase detectors are provided for maximum flexibility.

Proper partitioning of the loop function, with many of the building blocks external to the package, makes it easy for the designer to incorporate ripple cancellation or to cascade to higher order phase-locked loops.

The length of the up/down K counter is digitally programmable according to the K counter function table. With A, B, C, and D all low, the K counter is disabled. With A high and B, C, and D low, the K counter is only

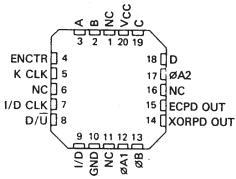

SN54LS297 . . . J OR W PACKAGE SN74LS297 . . . N PACKAGE (TOP VIEW) B 1 16 VCC 15 □ C 2 ENCTR [ 14 🛮 D 3 K CLK □4 13 ØA2 I/D CLK 5 12 ECPD OUT D/U∏6 11 XORPD OUT 10 ØB I/D OUT 7 GND 8 9 ØA1

SN54LS297 . . . FK PACKAGE (TOP VIEW)

NC-No internal connection

three stages long, which widens the bandwidth or capture range and shortens the lock time of the loop. When A, B, C, and D are all programmed high, the K counter becomes seventeen stages long, which narrows the bandwidth or capture range and lengthens the lock time. Real-time control of loop bandwidth by manipulating the A through D inputs can maximize the overall performance of the digital phase-locked loop.

Pin numbers shown are for J, N and W packages.

TEXAS INSTRUMENTS

#### description (continued)

The 'LS297 can perform the classic first-order phase-locked loop function without using analog components. The accuracy of the digital phase-locked loop (DPLL) is not affected by  $V_{CC}$  and temperature variations, but depends solely on accuracies of the K clock, I/D clock, and loop propagation delays. The I/D clock frequency and the divide-by-N modulos will determine the center frequency of the DPLL. The center frequency is defined by the relationship  $f_{C} = I/D$  Clock/2N (Hz).

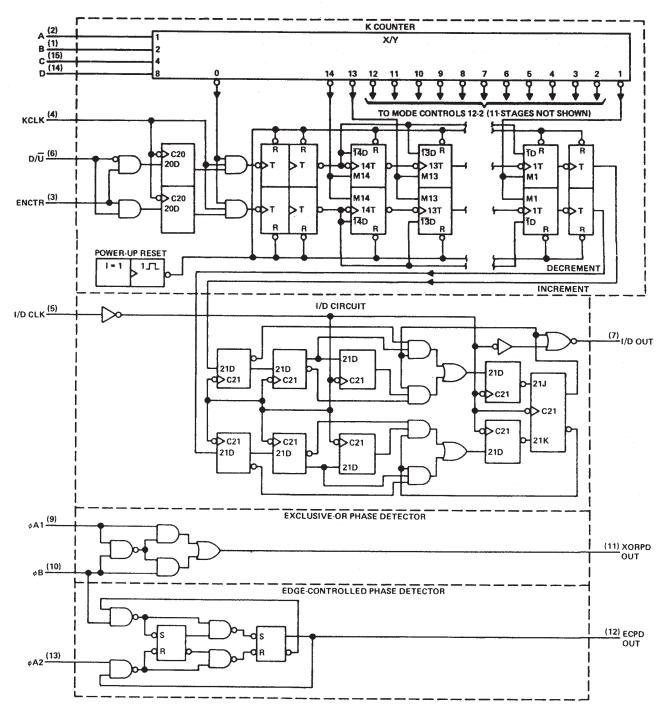

### logic diagram (positive logic)

Pin numbers shown are for J, N, and W packages.

## K COUNTER FUNCTION TABLE (DIGITAL CONTROL)

| - 1 |   |      |    |     |                                  |

|-----|---|------|----|-----|----------------------------------|

|     | D | С    | В  | Α   | MODULO (K)                       |

| -   | Ł | L    | L  | L   | Inhibited                        |

| -   | L | L    | L  | Н   | 23                               |

| ٠   | L | ٠. ٢ | H  | ∾ Ľ | 2 <sup>4</sup><br>2 <sup>5</sup> |

|     | L | Ł    | Н  | н   | 25                               |

|     | L | н    | L  | L   | 26                               |

| -   | L | н    | L  | Н.  | 27                               |

| İ   | L | н    | н  | L   | 28                               |

|     | Ł | н    | н  | н   | 29                               |

|     | Н | L    | L. | L   | 210                              |

|     | н | L    | L  | н   | 211                              |

|     | н | L    | н  | L   | 212                              |

| 1   | н | L    | н  | н   | 2 <sup>13</sup>                  |

|     | Н | н    | L  | L   | 214                              |

|     | н | н    | L  | н   | 215                              |

|     | н | н    | н  | Ļ   | 216                              |

|     | н | н    | н  | н   | 217                              |

|     |   | ł    | 1  | Į.  | I                                |

# FUNCTION TABLE EXCLUSIVE-OR PHASE DETECTOR

| φΑ1 | φВ | XORPD OUT             |

|-----|----|-----------------------|

| L   | L  | L                     |

| L   | н  | н                     |

| • н | L  | er Am <b>H</b> errier |

| н   | н  | · L                   |

## FUNCTION TABLE EDGE-CONTROLLED PHASE DETECTOR

| φ <b>А2</b> | φВ       | ECPD OUT  |

|-------------|----------|-----------|

| H or L      | 1        | н         |

| 4           | H or L   | L         |

| H or L      | <b>↑</b> | No change |

| 1           | H or L   | No change |

| 1           |          |           |

H = steady-state high level

L = steady-state low level

# = transition from high to low

t = transition from low to high

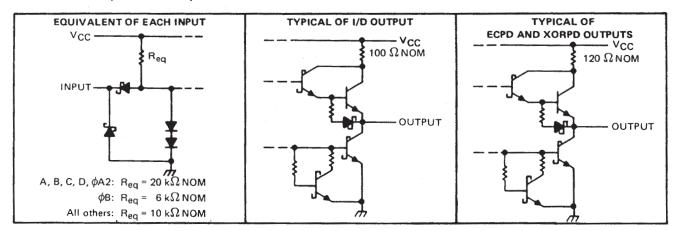

#### schematics of inputs and outputs

#### operation

The phase detector generates an error signal waveform that, at zero phase error, is a 50% duty cycle square wave. At the limits of linear operation, the phase detector output will be either high or low all of the time, depending on the direction of the phase error  $(\phi_{in} - \phi_{out})$ . Within these limits, the phase detector output varies linearly with the input phase error according to the gain  $k_d$ , which is expressed in terms of phase detector output per cycle of phase error. The phase detector output can be defined to vary between  $\pm 1$  according to the relation:

$$PD Output = \frac{\% high - \% low}{100}$$

(1)

The output of the phase detector will be  $k_d \phi_e$ , where the phase error  $\phi_e = \phi_{in} - \phi_{out}$ .

SDLS155 - JANUARY 1981 - REVISED MARCH 1988

Exclusive-OR phase detectors (XORPD) and edge-controlled phase detectors (ECPD) are commonly used digital types. The ECPD is more complex than the XORPD logic function, but can be described generally as a circuit that changes states on one of the transitions of its inputs.  $k_d$  for an XORPD is 4 because its output remains high (PD output = 1) for a phase error of 1/4 cycle. Similarly,  $k_d$  for the ECPD is 2 since its output remains high for a phase error of 1/2 cycle. The type of phase detector will determine the zero-phase-error point, i.e., the phase separation of the phase detector inputs for  $\phi_e$  defined to be zero. For the basic DPLL system of Figure 2,  $\phi_e$  = 0 when the phase detector output is a square wave. The XORPD inputs are 1/4 cycle out of phase for zero phase error. For the ECPD,  $\phi_e$  = 0 when the inputs are 1/2 cycle out of phase.

FIGURE 2-DPLL USING EXCLUSIVE-OR PHASE DETECTION

The phase detector output controls the up/down input to the K counter. The counter is clocked by input frequency  $Mf_C$ , which is a multiple M of the loop center frequency  $f_C$ . When the K counter recycles up, it generates a carry pulse. Recycling while counting down generates a borrow pulse. If the carry and borrow outputs are conceptually combined into one output that is positive for a carry and negative for a borrow, and if the K counter is considered as a frequency divider with the ratio  $Mf_C/K$ , the output of the K counter will equal the input frequency multiplied by the division ratio. Thus the output from the K counter is  $(k_d \phi_e Mf_C)/K$ .

The carry and borrow pulses go to the increment/decrement (I/D) circuit, which, in the absence of any carry or borrow pulse, has an output that is 1/2 of the input clock I/D CLK. The input clock is just a multiple, 2N, of the loop center frequency. In response to a carry or borrow pulse, the I/D circuit will either add or delete a pulse at I/D OUT. Thus the output of the I/D circuit will be Nf<sub>c</sub> +  $(k_d\phi_e Mf_c)/2K$ .

The output of the N counter (or the output of the phase-locked loop) is thus:

$$f_0 = f_c + (k_d \phi_e M f_c)/2KN$$

If this result is compared to the equation for a first-order analog phase-locked loop, the digital equivalent of the gain of the VCO is just  $Mf_c/2KN$  or  $f_c/K$  for M=2N.

Thus the simple first-order phase-locked loop with an adjustable K counter is the equivalent of an analog phase-locked loop with a programmable VCO gain.

FIGURE 3-DPLL USING BOTH PHASE DETECTORS IN A RIPPLE-CANCELLATION SCHEME

### absolute maximum rating over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)      |                                       | 7 V               |

|---------------------------------------|---------------------------------------|-------------------|

| Input voltage                         |                                       | 7 V               |

| Operating free-air temperature range: | SN54LS297                             | - 55° C to 125° C |

|                                       | SN74LS297                             | 0° C to 70° C     |

| Storage temperature range             | ************************************* | - 65° C to 150° C |

NOTE 1: Voltage values are with respect to network ground terminal.

#### recommended operating conditions

|                        |                                |            | S    | SN54LS297                               |       | SN74LS297 |     |               |      |

|------------------------|--------------------------------|------------|------|-----------------------------------------|-------|-----------|-----|---------------|------|

|                        |                                |            | MIN  | NOM                                     | MAX   | MIN       | NOM | MAX           | UNIT |

| Vcc                    | Supply voltage                 |            | 4.5  | 5                                       | 5.5   | 4.75      | 5   | 5.25          | V    |

| Юн                     | High-level output current      | I/D OUT    |      |                                         | - 1.2 |           |     | - 1.2         | mA   |

| 'UH                    | riigii-level output current    | EXOR, ECPD |      |                                         | - 400 |           |     | MAX<br>5 5.25 | μА   |

| loL                    | Low-level output current       | I/D OUT    |      |                                         | 12    |           |     | 24            | mA   |

| 'OL                    | Low-level output carrent       | XOR, ECPD  |      |                                         | 4     |           |     | 8             | mA   |

| fclock                 | Clock frequency                | K Clock    | 0    | *************************************** | 32    | 0         |     | 32            | MHz  |

| CIOCK                  |                                | I/D Clock  | 0    |                                         | 16    | 0         |     | 16            | MHz  |

| t <sub>w</sub>         | Width of clock input pulse     | K Clock    | 16   |                                         |       | 16        |     |               | ns   |

| ·W                     | Width of clock liput pulse     | I/D Clock  | 33   |                                         |       | 33        |     |               | ns   |

| t <sub>su</sub> , to K | Setup time to K Clock 1        | U/D;ENCTR  | . 30 |                                         |       | 30        |     | ***           | ns   |

| th                     | Hold time from K Clock †       | U/D, ENCTR | 0    |                                         |       | 0         |     |               | ns   |

| TA                     | Operating free-air temperature |            | - 55 |                                         | 125   | 0         |     | 70            | °C   |

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER                                |                                        | TEST CONDITIONS†                      |                                            | SN54LS297               |                       |      | SN74LS297 |       |      |                                       |       |    |

|------------------------------------------|----------------------------------------|---------------------------------------|--------------------------------------------|-------------------------|-----------------------|------|-----------|-------|------|---------------------------------------|-------|----|

|                                          |                                        | TEST CONDITIONS.                      |                                            |                         | MIN                   | TYP‡ | MAX       | MIN   | TYP‡ | MAX                                   | UNIT  |    |

| V <sub>IH</sub> High-level input voltage |                                        |                                       |                                            |                         |                       | 2    |           |       | 2    | teler it.                             |       | V  |

| VIL                                      | Low-level input vo                     | oltage                                |                                            |                         |                       |      |           | 0.7   |      |                                       | 0.8   | V  |

| VIK                                      | Input clamp volta                      | ge                                    | VCC = MIN,                                 | 1 <sub>1</sub> = -18 mA |                       |      |           | -1.5  |      |                                       | -1.5  | V  |

| VOH                                      | High-level                             | I/D OUT                               | VCC = MIN,                                 | V <sub>IH</sub> = 2 V,  | I <sub>OH</sub> = MAX | 2.4  |           |       | 2.4  |                                       |       |    |

| TOH                                      | output voltage                         | Others                                | VIL = VIL max                              |                         | IOH = MAX             | 2.5  |           |       | 2.7  |                                       |       | ٧  |

|                                          |                                        | I/D OUT                               |                                            |                         | IOL = 12 mA           |      | 0.25      | 0.4   |      | 0.25                                  | 0.4   |    |

| VOL                                      | Low-level                              | .,,,,,,                               | V <sub>CC</sub> = MIN,                     | V <sub>IH</sub> = 2 V,  | IOL = 24 mA           |      |           |       |      | 0.35                                  | 0.5   |    |

| .05                                      | output voltage                         | Others                                | VIL = VIL max                              | ■ V <sub>IL</sub> max   | IOL = 4 mA            |      | 0.25      | 0.4   |      | 0.25                                  | 0.4   | V  |

|                                          |                                        | Others                                |                                            |                         | IOL = 8 mA            |      |           |       |      | 0.35                                  | 0.5   |    |

| -t <sub>i</sub>                          | Input current at maximum input voltage |                                       | V <sub>CC</sub> = MAX,                     | V <sub>I</sub> = 7 V    |                       |      |           | 0.1   |      |                                       | 0.1   | mA |

|                                          | High-level                             | U/δ, EN, φΑ1                          | V <sub>CC</sub> = MAX, V                   |                         |                       |      |           | 40    |      |                                       | 40    |    |

| 1 <sub>1H</sub>                          | input current                          | φ <b>B</b>                            |                                            | V <sub>1</sub> = 2.7 V  |                       |      |           | 60    |      | · · · · · · · · · · · · · · · · · · · | 60    | μΑ |

|                                          | mpat carrent                           | All others                            |                                            |                         |                       |      |           | 20    |      |                                       | 20    |    |

|                                          | Low-level input current                | U/ $\bar{\mathbb{D}}$ , EN, $\phi$ A1 | V <sub>CC</sub> = MAX,                     | V. = 0.4 V              |                       |      |           | - 0.8 |      |                                       | - 0.8 |    |

| 11L                                      |                                        | φВ                                    | V <sub>1</sub> = 0.4 V                     | V1 = 0.4 V              |                       |      |           | -1.2  |      |                                       | -1.2  | mA |

|                                          |                                        | All others                            | V <sub>1</sub> 0.4 V                       |                         |                       |      |           | - 0.4 |      |                                       | - 0.4 |    |

| los                                      | Short-circuit                          | I/D OUT                               | Vac = MAY                                  |                         |                       | -30  |           | -130  | 30   |                                       | -130  | ^  |

| .03                                      | output current §                       | Others                                | V <sub>CC</sub> = MAX                      |                         |                       | -20  |           | -100  | -20  |                                       | -100  | mA |

| Icc                                      | Supply current                         |                                       | V <sub>CC</sub> = MAX,<br>All outputs open | All inputs gro          | unded,                |      | 75        | 120   |      | 75                                    | 120   | mA |

<sup>&</sup>lt;sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

## switching characteristics, $V_{CC}$ = 5 V, $T_A$ = 25°C

| PARAMETER¶       | FROM (INPUT)          |                  | FROM (INPUT) TO (OUTPUT) TEST CONDITIONS |                         | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------|-----------------------|------------------|------------------------------------------|-------------------------|-----------------|-----|-----|-----|------|

| fmax             | KCLK                  |                  | I/D OUT                                  | R <sub>L</sub> = 667 Ω, | 32              | 50  |     |     |      |

| ¹max             | I/D CLK               |                  | I/D OUT                                  |                         | 16              | 35  |     | MHz |      |

| tPLH I/D CLK †   |                       |                  | I/D OUT                                  | CL = 45 pF,             |                 | 15  | 25  | ns  |      |

| tPHL.            | I/D CLK †             |                  | I/D OUT                                  | See Note 2              |                 | 22  | 35  | ns  |      |

| tnu              | $\phi$ A1 or $\phi$ B | Other input low  | XOR OUT                                  |                         |                 | 10  | 15  |     |      |

| <sup>t</sup> PLH | φΑ1 or <b>φ</b> Β     | Other input high | XOR OUT                                  | Rլ= 2kΩ,                |                 | 17  | 25  | ns  |      |

| tour             | $\phi$ A1 or $\phi$ B | Other input low  | XOR OUT                                  |                         |                 | 15  | 25  |     |      |

| tPHL -           | φΑ1 or <b>φ</b> Β     | Other input high | XOR OUT                                  | C <sub>L</sub> = 45 pF, |                 | 17  | 25  | ns  |      |

| tPLH             | φB ↓                  |                  | ECPD OUT                                 | See Note 2              |                 | 20  | 30  | ns  |      |

| tPHL             | φ <b>A</b> 2↓         |                  | ECPD OUT                                 |                         | <del></del> -   | 20  | 30  | ns  |      |

$<sup>\</sup>mathbf{1}_{tpLH}$  = propagation delay time, low-to-high-level output

$<sup>\</sup>ddagger$ All typical values are of  $V_{CC}$  = 5 V,  $T_{A}$  = 25°C.

<sup>§</sup> Not more than one output should be shorted at a time and the duration of the short-circuit should not exceed one second.

tpHL = propagation delay time, high-to-low-level output

NOTE 2: Load circuits and voltage waveforms are shown in Section 1.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated